# Partial Filter Duplication: A Solution for Noise Tolerant FIR Filter

Antonio Mollfulleda San Julián

Telecommunications Technologial Center of Catalonia

(CTTC),

C/ Gran Capità, 2-4,

Edifici Nexus I – Office 202, 203

08034 Barcelona (Spain)

antonio.mollfulleda@cttc.es

Fernando Casadevall Palacio

Dept. of Signal Theory and Communications,

Polytechnic University of Catalonia (UPC),

C/ Jordi Girona 1-3

mòdul D4 – Campus Nord UPC

08034 Barcelona (Spain)

ferran@xaloc.upc.es

Abstract--As a result of the new trends in semiconductor technology using the new scale of integration, the current design tools and methodologies cannot provide a reliable medium for digital circuit implementation due to the existence of Deep Submicron (DSM) noise. Then, there are two groups of solutions to protect linear operations, such as FIR filters, from technology noise. The First one consists of protecting the data in operations, such as addition or multiplication, using coding theory. The second one treats the problem from an algorithmic point of view, which is known as Algorithmic Noise Tolerant (ANT). The most popular ANT for linear filters is Soft-DSP, which is based on a linear predictor to perform a parallel estimation of the filter output, understood as additional information to protect the original filter operation. This paper proposes an alternative algorithm for Parallel-Estimation ANT (PE-ANT) in which the original filter is partially duplicated. Simulation results show that this approach has better performance under bad noise conditions.

*Keywords*: Fault Tolerant, Algorithmic Noise Tolerant, Deep Submicron Noise, DSM, FIR Filter.

### I. INTRODUCTION

The application of sophisticated digital signal processing techniques for communications, such as multi-user detection or smart antenna algorithms, imposes a stringent demand on hardware implementation. This increase on computational complexity requires the use of the new scale of integration in order to provide System on a Chip (SoC) solution. On the other hand, the current semiconductor technology, design tools and methodologies cannot achieve an enough level of noise-immunity so as to consider the new technologies as a reliable medium [1][2]. This situation leads to a new design context in communication systems, which should face both problems: the reliability of communication under noisy channel and reliability of computation in a unreliable medium.

The problem of guarantying a reliable computation with elements that themselves are unreliable was firstly analyzed in some times ago by Von Newman, Shannon and Moore from an information theory point of view [3][4]. Later the equivalence between a reliable communication and a reliable computation was shown in [5]. This work leads to the introduction of the concept of computation capacity defined as the maximum rate for computing with an arbitrary high reliability. Recently, a mathematical basis to treat the problem from an information theory point of view, which has lead to solutions that are appropriate for digital signal processing, has been presented in [6].

During the last decades the solutions to achieve reliability can be divided in two big groups. The first one, which is called Algebraic Data Integrity (ADI), is based on the application of algebraic error protecting codes to data operands. These codes are applied to linear operations such as addition or multiplication. Arithmetic Codes [7] and Redundant Residue Number System (RRNS) codes [8][9] as approaches that belong to this group. The second group, known as Algorithmic Noise Tolerant (ANT) solutions, apply noise protection from an algorithmic point of view, without considering the error in each specific operation. In this case, the level of protection provided by the solution depends on the algorithm architecture. One of the main differences between both approaches is that ADI tries to protect all bits of the result in each single operation while ANT tries to keep the algorithm performance at an acceptable level.

The ANT solution for FIR filters, known as Soft-DSP, is presented in [10]. This approach is based on the estimation of the filter output using linear prediction. Therefore, this solution can be classified in the group that addresses ANT by performing a parallel estimation of the filter output (PE-ANT). In this paper we propose a new algorithm for this group of solutions, which deals with the duplication of some filter coefficients to achieve better performance, particularly when high level of noise is found in the technology elements.

The paper is organized as follows. Section II describes the concepts behind generic parallel estimation ANT and introduces the system model used in this work. Section III describes the previous work on Soft-DSP whereas in section IV the proposed PE-ANT is presented. Section V shows the results after applying both algorithms on a digital low pass filter used for IF downconversion in a WLAN system. Finally, section VI exposes the conclusions of the paper.

### II. PARALLEL ESTIMATION ANT

In order to highlight the advantages of the proposed solution, consider a FIR filter to be used in a digital downconverter. The filter is assumed to be implemented using an scale of integration in which the DSM Noise affects the reliability of the filter operation. The system is modelled as a reliable filter with noise added at the output of the filter. Since there is no statistic model of noise in DSM, the model used assumes that any bit of each output sample in the filter can be incorrect with probability  $P_{err}$ , [10]. Thus, the noise filter can be modelled by means of equation (1).

$$y_{e}(n) = y(n) + w(n) = \sum_{k=0}^{N-1} h(k) \cdot x(n-k) + w(n)$$

(1)

x(n) denotes the input signal, y(n) is the noiseless output signal,  $y_e(n)$  is the noise affected output, h(n) are the filter coefficients, N is the number of taps of the filter and w(n) represents the DSM noise equivalent at the output of the filter.

As for the case of communication systems, the noise level can be expressed as the Signal-to-Noise Ratio (SNR) at the output of the filter. Therefore, the main goal of ANT is to maintain the output SNR to an acceptable level for each application.

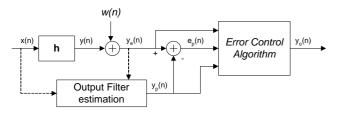

Fig. 1. shows the system model for a generic (PE-ANT) solution. This technique performs an estimation of the filter output. The data used for error estimation can be either the previous filter output, the filter input signal or both. Then, the estimated output,  $y_p(n)$ , and the noise-added output are processed in the error control block to provide the noise protected samples. Notice that the output is not completely free of error, but it must keep the Signal-to-Noise Ratio (SNR) at an acceptable level depending on each application. Therefore the error control block is designed to increase the SNR at the filter output. Notice also that the estimator is assumed to be free of error. This assumption is feasible by using redundant ADI or simply circuit replication techniques for error protecting as long as the complexity of the estimator could be maintained lower than the original filter.

Fig. 1. Parallel Estimation ANT.

### III. SOFT-DIGITAL SIGNAL PROCESSING

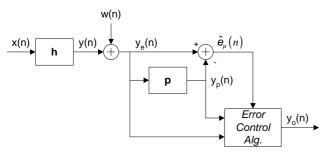

Soft Digital Signal Processing is a PE-ANT approach, which is based just on the previous filter output to perform a linear prediction [10]. Fig. 2 shows the scheme used in Soft-DSP. In digital communication systems the signal is usually correlated and thus, the low-pass filtering of these signals generates a process that can be easily predicted using a low order predictor [11]. Equation (2) denotes the expression of the predictor output.

$$y_p(n) = \sum_{k=0}^{NP-1} y_e(n-k) \cdot p(k)$$

(2)

where p(k) are the predictor coefficients and NP is the predictor order. The predictor coefficients are calculated to minimize the mean squared error (MMSE) between the noiseless filter output, y(n), and the predictor.

Notice that the last NP samples of the filter output are assumed to be correct in order to have good signal estimation. Since this assumption is not necessarily valid for a system with noise coming from the used technology, Soft-DSP includes an Error Control Algorithm (ECA) to reduce the effect of error propagation for the case when an error occurs in the original filter. This algorithm assumes that at most one error occurs in a span of  $2 \cdot NP$  samples. Then, an error vector is formulated as follows:

$$\hat{\mathbf{e}}_{p}(n) = w(n) \cdot \mathbf{p} + \mathbf{e}_{p}(n)$$

(3)

where

$$\hat{\mathbf{e}}_{p}(n) = \begin{bmatrix} \hat{\mathbf{e}}_{p}(n) & \hat{\mathbf{e}}_{p}(n+1) & \cdots & \hat{\mathbf{e}}_{p}(n+NP) \end{bmatrix}^{T}

\mathbf{p} = \begin{bmatrix} 1 & -p(1) & -p(2) & \cdots & -p(NP) \end{bmatrix}^{T}

\mathbf{e}_{p}(n) = \begin{bmatrix} e_{p}(n) & e_{p}(n+1) & \cdots & e_{p}(n+NP) \end{bmatrix}^{T}$$

$\hat{e}_p(n)$  represents the total estimation error,  $e_p(n)$  is the prediction error and w(n) is the error introduced by DSM noise.

Given Equation (3), the ECA defined in Soft-DSP is described in the following lines:

- Let  $\sigma_p^2$  be the variance of the prediction error with noiseless digital filter.

- An error is detected if

$$\left|\mathbf{p}^{T}\cdot\hat{\mathbf{e}}_{p}\left(n\right)\right|>\mathbf{S}_{p}^{2}\tag{4}$$

• If an error is detected  $y_o(n) = y_p(n)$  else  $y_o(n) = y_e(n)$

Notice that the performance of Soft-DSP depends on the decision threshold for error detection and on the assumption that  $y_e(n)$  is relatively large compared to  $y_p(n)$ . This forces to know a priori the statistics of the error magnitude and then fix an adequate threshold to achieve the required performance. Unfortunately, in practice this knowledge is not always available.

Another important limitation is that the performance of Soft-DSP deteriorates when multiple error occurs in a span of  $2 \cdot NP$  samples of the original filter. As a consequence, this algorithm can only be applicable when the frequency of errors in the original filter is less than  $1/(2 \cdot NP)$ . Finally, notice that the complexity required to carry out the predictor filter and the ECA is  $2 \cdot NP$  operations.

Fig. 2. Soft-DSP scheme.

### IV. PARTIAL FILTER DUPLICATED PREDICTION

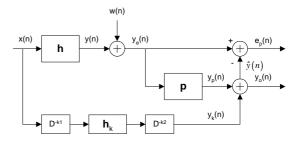

The first approach considered in this work is to reduce the predictor order to have just one coefficient and thus improve the estimator variance by duplicating part of the filter. Fig. 3 shows the scheme of the proposed Partial Filter Duplicated ANT (PFD-ANT). The symbol  $D^k$  represents a k-sample delay, which is introduced to synchronize the estimated signal with the output filter. In this approach, the output filter estimation is generated by the addition of two signals: the output of the partially duplicated filter and the result of a linear prediction, which order is one. The duplicated filter coefficients should be those with maximum absolute value. In that way, a better estimation performance is obtained.

The estimated signal can be expressed as in equation (5).

$$\hat{y}(n) = \sum_{j=k}^{k+L-1} h(k) \cdot x(n-k) + a \cdot y_e(n-1)$$

(5)

where k and L are respectively the first tap of the original filter and the number of coefficients to be duplicated.  $\boldsymbol{a}$  denotes the predictor tap that is calculated for minimizing the minimum squared error (MMSE) between the estimated signal and the noiseless filter output, as shown in the following equations,

$$\mathbf{e}_{\mathbf{y}}(n) = \mathbf{y}(n) - \hat{\mathbf{y}}(n) \tag{6}$$

$$\boldsymbol{a} = \frac{1}{r_{v}(0)} \cdot \left( r_{y}(1) - \mathbf{r}_{yx}^{T} \cdot \mathbf{h}_{k} \right)$$

(7)

where

$$\mathbf{r}_{yx} = \begin{bmatrix} r_{yx} \left( -k \right) & r_{yx} \left( -k+1 \right) & \cdots & r_{yx} \left( -k+L-1 \right) \end{bmatrix}^{T}$$

(8)

$$\mathbf{h}_{\mathbf{k}} = \begin{bmatrix} h(k) & h(k+1) & \cdots & h(k+L-1) \end{bmatrix}^{T}$$

(9)

In this case, the predictor order is reduced to one coefficient and thus, the ECA can be simplified or even eliminated because the effect of error propagation is highly reduced. In fact, as shown in section V, in practical situations the estimated output has a noise level that can be tolerated in many digital signal processing applications. Finally, in terms of complexity the PFD-ANT requires L+1 computations.

Fig. 3. Partial Filter Duplicated ANT.

### V. APPLICATION EXAMPLE

### A. Simulation Model

The application of the proposed PFD-ANT model is performed in a filter used in a digital downconverter. Therefore the filtered signal is a band limited signal, which is corrupted by Additive Gaussian Wideband Noise (AGWN). Unfortunately for digital filters, no specific DSM noise model is currently available. As a result we propose to use two simplified different noise models to test the performance of both approaches. The first model assumes that any bit of each output sample can be incorrect with a probability of error  $P_{err}$ . In this model there are no statistical dependencies between the errors of different output samples and thus the error model is characterized by independent single errors.

The second approach for error modelling takes into account the memory of the filter operation, i.e., if an error occurs in an internal stage of the filter operation, then this error affects to several output samples. Notice that in this model there is statistical dependence between consecutive samples of the error signal. As a consequence, this error model is mainly characterized by burst errors.

The next two subsections show the performance achieved for the two described algorithms when both noise models are applied. The results are presented as a function of the SNR in the original filter (without any compensation), which will be referred as original SNR.

# B. Results for Uncorrelated Error Model

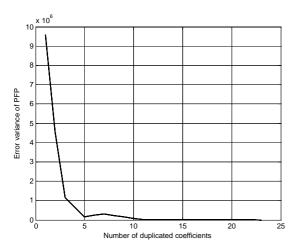

For the single error model, the bit error probability,  $P_{err}$ , ranges between  $10^{-1}$  and  $10^{-5}$ , and it models different signal to noise ratio at the output of the original filter. The number of coefficients to be duplicated in PFD-ANT is set to assure that the signal  $y_k(n)$  contributes with an estimation of about the 70% of the original output. Fig. 4

shows the error variance of partial filter duplicated as a function of the duplicated taps. It is shown that the error variance becomes relatively small when at least the three taps with maximum absolute value are duplicated.

Fig. 4. Error variance of Partial Duplicated Filter.

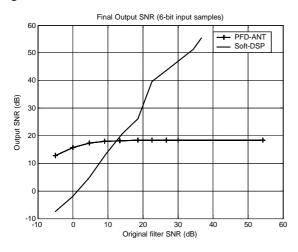

Fig. 5 depicts the final output SNR applying both, Soft-DSP and PFD-ANT algorithms. The input signal is quantified using 6 bits, the order of the predictor in Soft-DSP is set to NP = 3 and the number of replicated coefficients in PFD-ANT is L = 3. Notice that, in this case, the complexity of PFD-ANT estimator is 4 operations while the complexity of Soft-DSP is 6 operations.

The results show that PFD-ANT improves the output SNR even with negative original SNR, while Soft-DSP cannot offer significant improvements for original SNR below 10dB. This is because in the range below 10dB the probability that two or more errors occur in a span of  $2 \cdot NP$  becomes relevant. In contrast, notice that PFD-ANT keeps constant the output SNR even though it does not offer significant improvements for high values of the original SNR.

Fig. 5. Comparison between Soft-DSP (NP = 3) and PFD-ANT (L = 3) using uncorrelated error model.

## C. Result for Correlated Error Model

For the correlated error model, the bit error probability at the output of each internal single operation of the filter,  $P_{err}$ , also ranges between  $10^{-1}$  and  $10^{-5}$ .

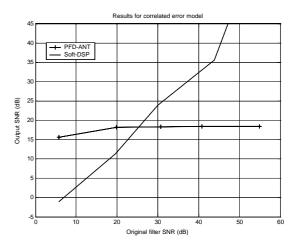

Fig. 6. shows the obtained result when using the correlated error model. In this situation, the memory of the filter causes that an error in an internal stage affects to several output samples. Notice that the proposed PFD-ANT solution is robust against correlated burst errors mainly because of two reasons: first, the output of the partial duplicated filter contributes with a noiseless signal, which represents about the 70% of the original output; second, the predictor order is reduced to order one and thus, the error propagation is limited. In contrast, the performance of the Soft-DSP approach deteriorates the output SNR due to the presence of burst errors.

Fig. 6. Comparison between Soft-DSP (NP = 3) and PFD-ANT (L = 3) using correlated error model.

# VI. CONCLUSIONS

The future trends in semiconductor technology, that contemplates the reduction of the scale of integration, cannot assure a reliable medium to implement digital systems due mainly to the effects of Deep Submicron (DSM) noise. This paper has presented a design methodology of a FIR filter, which is robust against DSM noise. The solution proposed is based on Algorithmic Noise Tolerant (ANT) strategy applied to digital signal processing applications known as Soft-DSP. The proposed system, called Partial Filter Duplication ANT (PFD-ANT) also protects the original filter by performing an estimation of the filter output. In particular, the presented solution performs an estimation based on linear prediction of order one and partial duplication of the original filter coefficients. The duplicated taps must be those with the highest absolute value.

A low-pass filter used in a digital downconverter affected with DSM noise was simulated to test the performance of PFD-ANT. Simulation results show that for SNR values (at the output of the original filter) below 15dB, the final achieved SNR keeps a minimum value of

about 18dB, which can be considered good enough in many situations of digital communication systems. Simulations also show that PFD-ANT maintains the performance when burst errors occurs at the output of the original filter, giving a robust solution for a bad conditioned environment.

### **ACKNOWLEDGEMENT**

The authors whish to thank J. Rodriguez for reading the paper and for his helpful comments on the work.

This work was partially supported by the European Program EUREKA – MEDEA + (Label A111) and partially funded by the Spanish government under contract FIT-070000-2003-257.

# REFERENCES

- K. Shepard, "Conquering noise in deep submicron digital ICs", IEEE Design and Test Computers, Jan-Mar. 1998, pp. 51-62.

- [2] R. E. Bryant, K.-T. cheng, A. B. Kahng, K. Keutzer, W. Maly, R. Newton, L. Pileggi, J. M. Rabaey, A. Sangiovanni-Vicentelli, "Limitations and Challenges of Computer-Aided Design Technology for CMOS VLSI", Proceedings of the IEEE, Vol. 89, No. 3, March 2001, pp. 341-365.

- [3] J. Von Newmann, "Probabilistic Logics and Synthesis of Reliable Organism from Unreliable Components", pp. 43-98 in Automata Studies, C.E. Shannon and J. Mc-Carthy editors, Annals of Math. Studies, 34, Princeton Univ. Press (1956).

- [4] E.F. Moore, C.E. Shannon, "Reliable Circuits Using Less Reliable Relays", Jour. Franklin Inst. 262, 191-208 and 281-297 (1956).

- [5] P. Elias, "Computation in the Presence of Noise", IBM Journal, Oct. 1958.

- [6] N. R. Shanbhag, "Mathematical basis for Power-Reduction in Digital VLSI Systems", IEEE Trans. On Circuits and Systems II: Analog and Digital Signal Processing, Vol.44, No. 11, Nov. 1997.

- [7] T.R.N. Rao, *Error Coding For Arithmetic Processors*, Academic Press, New York and London, 1974.

- [8] H. Krishna, K-Y. Lin J-D. Sun, "A Coding Theory Approach to Error Control in Redundant Residue Number systems – Part: Theory and single Error correction", IEEE Trans on Circuits and systems II: Analog and Digital signal Processing, Vol. 39, No. 1, Jan. 1992.

- [9] J-D. Sun, H- Krishna, "A Coding Theory Approach to Error Control in Redundant Residue Number systems – Part II: Multiple Error Detection and correction", IEEE Trans. On Circuits and Systems II: Analog and Digital signal Processing, vol. 39, No. 1, Jan. 1992.

- [10] R. Hedge, N.R. Shanbhag, "Soft Digital Signal Processing", IEEE Trans. On VLSI Systems, Vol. 9, No. 6, Dec. 2001.

- [11] S. M. Kay, Fundamentals of Statistical Signal Processing, Volume I: Estimation Theory, Prentice Hall PTR., 1993.